# APÊNDICE A **Resumo Teórico**

## 1 CIRCUITOS BIESTÁVEIS

Há dois aspectos importantes a serem considerados a respeito de circuitos biestáveis (*flip-flops*): o tipo de *sincronismo* e o tipo de *controle*.

Com base nestes dois aspectos é possível classificar os biestáveis com relação ao:

#### • tipo de sincronismo:

- sensíveis ao nível do sinal de relógio (\*)

- sensíveis à borda do sinal de relógio

- sensíveis à largura do pulso de relógio (mestre-escravos)

(\*) geralmente denominados latches e não flip-flops.

#### • tipo de controle:

- tipo R-S (ou S-R ou set-reset)

- tipo D

- tipo J-K

O biestável mais simples é a célula básica R-S. Apesar de não possuir nenhum sinal de sincronismo, é considerado um dispositivo sensível ao nível.

A seguir apresentam-se os biestáveis de acordo com o tipo de sincronismo e, dentro de cada categoria, seus vários tipos de controle.

#### 1.1 Biestáveis Sensíveis ao Nível

## 1.1.1 Célula Básica (R-S Latch)

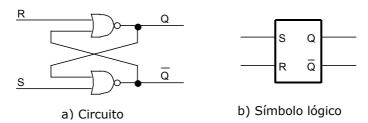

A figura 1.1 apresenta o biestável R-S construído a partir de portas NOR.

Figura 1.1 - Biestável R-S (Positivo).

A tabela I apresenta o comportamento desse dispositivo.

Tabela I - Tabela do Biestável R-S (Positivo).

| S | R     | Q(t) | Q(t+1) | Estado    |

|---|-------|------|--------|-----------|

| 0 | 0     | 0    | 0      | Popouso   |

| U | 0 1 1 |      | 1      | Repouso   |

| 0 | 1     | 0    | 0      | Docat     |

|   |       | 1    | 0      | Reset     |

| 1 | 0     | 0    | 1      | Set       |

| 1 |       | 1    | 1      | Set       |

| 1 | 1     | 0    | 0      | Não       |

|   |       | 1    | 0      | Permitido |

Considerando a Tabela I, obtém-se que Q(t+1) = S + R'.Q(t), onde R' significa R complementado (invertido) e considerando-se, é claro, que não se pode operar no estado não permitido. Observação:  $\overline{R} = R', \overline{S} = S', \overline{Q} = Q'$ , e assim por diante.

Para a análise do comportamento do R-S apresentado, pode-se supor que serão aplicadas, seqüencialmente, as seguintes combinações de valores lógicos nas entradas:

- 1. S = 0 e R = 0: nessa situação, os valores atuais de Q e Q' se mantêm, ou seja, Q(t+1) = Q(t) e Q'(t+1) = Q'(t);

- 2.  $\underline{S} = \underline{0} \ e \ R = \underline{1}$ : nessa situação, independentemente dos valores atuais de Q e Q', impõem-se novos valores às saídas, ou seja, Q(t+1) = 0 e Q'(t+1) = 1;

- 3. S = 1 e R = 0: nessa situação, independentemente dos valores atuais de Q e Q', impõem-se novos valores às saídas, ou seja, Q(t+1) = 1 e Q'(t+1) = 0;

- 4. S = 1 e R = 1: nessa situação, independentemente dos valores atuais de Q e Q', impõem-se às saídas Q(t+1) e Q'(t+1) o valor 0 . Esse fato acarreta três problemas:

- sendo as saídas designadas por Q e Q', espera-se que elas nunca assumam valores iguais;

- se as duas portas apresentassem atrasos exatamente iguais e se, após a situação em que S = R = 1, as entradas mudassem simultaneamente para S = R = 0, o circuito oscilaria;

- se as duas portas apresentassem atrasos diferentes, o comportamento do circuito seria imprevisível.

O biestável R-S se caracteriza como elemento de memória pois, ao observar uma de suas saídas (Q ou Q'), é possível saber qual das duas entradas apresentou valor igual a 1 lógico pela última vez. Assim, se no instante atual a saída Q=1, sabe-se que a entrada S assumiu valor 1, em algum instante passado, e que, a partir daquele instante a entrada R permaneceu sempre igual a zero. O biestável apresentado na Figura 1.1 é conhecido por R-S positivo, pois são níveis lógicos iguais a 1 em R ou em S que alteram o seu estado. É também possível construir um biestável R-S a partir de portas NAND, como mostrado na Figura 1.2.

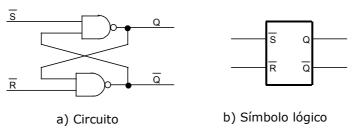

Figura 1.2 - Biestável R-S (Negativo).

O comportamento desse circuito é análogo ao anterior, negando-se os níveis das entradas. Nesse caso Q(t+1) = S+R'.Q(t) (desconsiderando-se o estado proibido), e esse biestável R-S é chamado de negativo, pois são os níveis lógicos iguais a 0 que alteram o seu estado. A tabela II resume o comportamento do biestável R-S negativo.

| $\overline{S}$ | $\overline{R}$ | Q(t) | Q(t+1) | Estado    |

|----------------|----------------|------|--------|-----------|

| 0              | 0              | 0    | 1      | Não       |

|                |                | 1    | 1      | Permitido |

| 0              | 1              | 0    | 1      | Set       |

|                |                | 1    | 1      |           |

| 1              | 0              | 0    | 0      | Reset     |

|                |                | 1    | 0      |           |

|                |                | 0    | 0      |           |

Repouso

Tabela II - Tabela do Biestável R-S (Negativo).

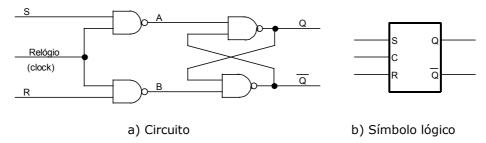

#### 1.1.2 Biestável R-S com Relógio

Muitas vezes é conveniente operar o biestável apenas em intervalos pré-determinados de tempo e deixar que suas saídas permaneçam inalteradas em outros, independentemente de variações nas entradas R e S.

A figura 1.3 apresenta o R-S com relógio, no qual as entradas somente atuam quando o sinal do relógio for igual a 1; quando o sinal do relógio for igual a 0, impõem-se A=B=1, que é o nível lógico de repouso do biestável e, portanto, as entradas S=R não mais atuam nas saídas. Nesse dispositivo, também não são permitidas ambas as entradas iguais a 1, enquanto o nível do sinal de relógio for igual a 1.

Figura 1.3 - Biestável R-S com Relógio.

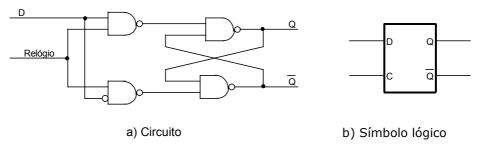

#### 1.1.3 Biestável tipo D, sensível ao nível (D-Latch)

Uma maneira de evitar o estado indeterminado do biestável R-S, quando as entradas assumem valores não permitidos, é a construção de um biestável com apenas uma entrada. A figura 1.4 apresenta tal dispositivo.

Figura 1.4 - Biestável tipo D, Sensível ao Nível.

Enquanto o sinal de relógio estiver no nível lógico 1, o sinal presente na entrada D é transferido para a saída Q. Quando o sinal de relógio cai para o nível lógico 0, o último valor presente na entrada D fica armazenado na saída Q; durante o intervalo em que o sinal de relógio permanece no nível lógico 0, variações na entrada D não são transferidas para a saída.

A figura 1.5 apresenta o comportamento do biestável D, sensível a nível.

Figura 1.5 - Comportamento do Biestável tipo D, Sensível ao Nível.

Outra possível implementação do biestável tipo D, sensível ao nível, é mostrada na Figura 1.6.

Figura 1.6 - Circuito Alternativo para o Latch tipo D.

## 1.2 Biestáveis Mestre-Escravo

Em biestáveis com relógio (síncronos), existe um nível do relógio no qual as portas de entrada são desativadas e, portanto, o biestável fica isolado dos dados presentes em seus terminais de entrada (conforme os itens 1.1.2 1.1.3). Um tipo de biestável que responde quando o relógio efetua uma transição para o nível de desativação é o Biestável Mestre-Escravo. Atualmente, os biestáveis mestre-escravo são pouco utilizados. Deste modo, será mencionado apenas o princípio utilizado na sua concepção.

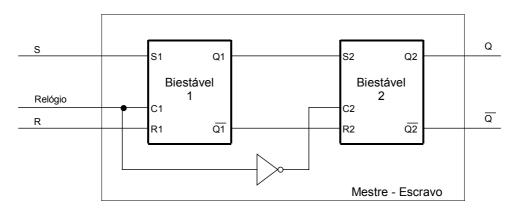

O biestável mestre-escravo emprega dois biestáveis com relógio, um chamado mestre e o outro, escravo, conforme mostrado na figura 1.7. O relógio do escravo é o complemento do relógio do mestre; deste modo, quando o mestre estiver ativado, o escravo não estará, e vice-versa.

Figura 1.7 - Diagrama Resumido de um Biestável Mestre-Escravo.

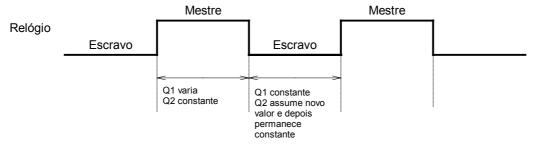

Quando o sinal de relógio for igual a 1, o mestre fica ativado e alterações nas entradas R e S se refletem na saída Q1. Entretanto, como o escravo (biestável 2) está desativado (C2 = 0), as saídas Q e Q' do dispositivo se mantêm constantes. Quando o sinal de relógio passar para 0, o mestre armazena, em Q1 e Q1', valores compatíveis com as entradas S e R presentes imediatamente antes da transição do relógio, mantendo-os inalterados. Nesta situação, como o escravo fica ativado (C2 = 1), os valores presentes em Q1 e Q1' serão adequadamente transferidos para as saídas Q e Q' do dispositivo. A figura 1.8 resume o que foi exposto.

Figura 1.8 - Comportamento do Biestável Mestre-Escravo.

Concluindo, deve-se ressaltar que a característica principal dos biestáveis mestre-escravo é que todas as alterações que eventualmente devem ser realizadas nas saídas do dispositivo somente ocorrerão quando o relógio efetuar a transição para o nível lógico 0, mantendo-se inalteradas nos outros instantes.

#### 1.3 Biestáveis Sensíveis à Borda

Dependendo das aplicações em que serão utilizados os biestáveis, é necessário que suas saídas armazenem os valores presentes nas entradas em instantes bem determinados do tempo, e que mantenham esses valores, independentemente de eventuais variações nas entradas.

Duas soluções poderiam ser pesquisadas:

- adoção das configurações mostradas nos itens 1.1.2 e 1.1.3, utilizando sinais de relógio constituídos de pulsos muito estreitos;

- adoção da configuração mestre-escravo, descrita no item 1.2.

Nenhuma dessas soluções, entretanto, foi adotada, pois, aplicando-se técnicas de projetos de circuitos seqüenciais, foi possível obter soluções que apresentem o comportamento desejado, com um menor número de portas.

### 1.3.1 Biestável tipo D, Sensível à Borda

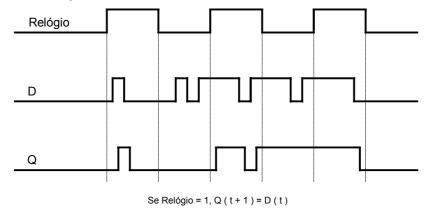

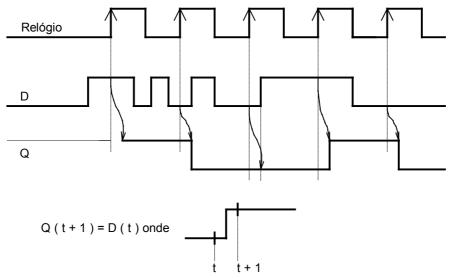

Um biestável tipo D sensível à borda (por exemplo, borda de subida) é aquele em que o sinal presente na entrada D é copiado na saída Q quando o sinal de relógio sobe, permanecendo armazenado até a próxima borda de subida. Eventuais variações da entrada D entre as bordas de subida não alteram a saída do dispositivo. A figura 1.9 resume esse comportamento.

Figura 1.9 - Comportamento de um Biestável tipo D, Sensível à Borda de Subida.

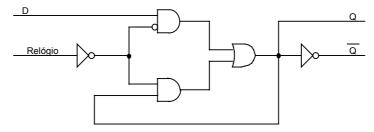

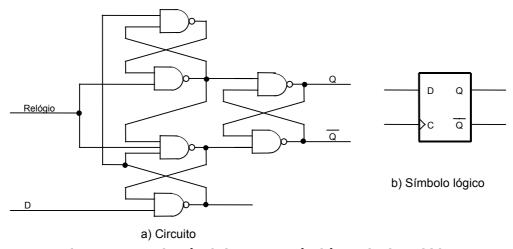

Na Figura 1.10 apresenta-se o circuito, construído com portas NAND, do biestável tipo D, sensível à borda de subida. O circuito mostrado é aquele adotado na implementação dos biestáveis integrados tipo D, sensíveis à borda.

Figura 1.10 - Biestável tipo D, Sensível à Borda de Subida.

## 1.3.2 Biestável J-K, Sensível à Borda

Os biestáveis J-K surgiram como solução para contornar o problema de valores proibidos para as entradas set e reset (J-K com relógio e J-K mestre-escravo). Entretanto, a única configuração de J-K que realmente vem sendo utilizada é a do J-K sensível à borda. A tabela III descreve o seu comportamento.

Tabela III - Tabela do Biestável J-K, Sensível à Borda de Subida.

| J(t) | K(t) | Q(t+1)* | Estado  |

|------|------|---------|---------|

| 0    | 0    | Q(t)    | Mantém  |

| 0    | 1    | 0       | Reset   |

| 1    | 0    | 1       | Set     |

| 1    | 1    | Q'(t)   | Inverte |

<sup>\*</sup> t = instante que antecede a borda de subida do relógio t+1 = instante seguinte à borda de subida do relógio

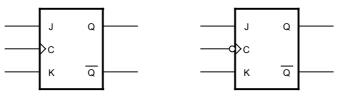

Na Figura 1.11, mostram-se os símbolos lógicos utilizados para representar esse biestável.

a) Borda de subida

b) Borda de descida

Figura 1.11 - Representação de Biestáveis J-K Sensíveis à Borda.

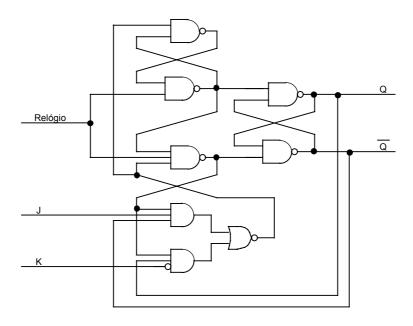

O circuito, construído com portas, que é utilizado na sua implementação, é mostrado na Figura 1.12.

Figura 1.12 - Biestável J-K, Sensível à Borda de Subida.

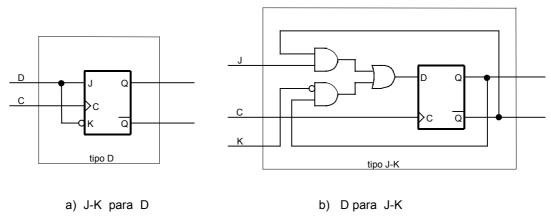

O Biestável J-K, sensível à borda, pode ser utilizado como um tipo D, sensível à borda, através da configuração mostrada na Figura 1.13 (a). É também possível transformar um biestável tipo D em J-K, conforme mostrado na Figura 1.13(b).

Figura 1.13 - Transformações J-K x D (ambos sensíveis à borda de subida).

## 1.3.3 Biestável tipo T (Toggle Flip-Flop)

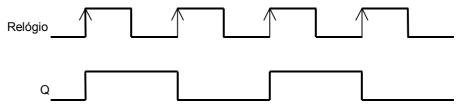

O biestável tipo T é aquele em que a saída Q muda de estado em todas as bordas de subida do relógio (ou então em todas as bordas de descida). O seu comportamento é mostrado na Figura 1.14.

Figura 1.14 - Comportamento do Biestável Tipo T (sensível à borda de subida).

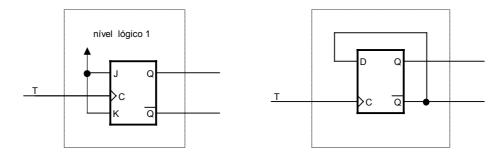

Um biestável tipo T pode ser obtido conforme mostra a figura 1.15.

- a) com J-K, borda de subida

- b) com tipo D, borda de subida

Figura 1.15 - Biestáveis Tipo T, Sensível à Borda de Subida.

## 1.4 Biestáveis Integrados

Todos os biestáveis descritos nos itens anteriores, com exceção do tipo T e do R-S com relógio, são disponíveis na forma de circuitos integrados, com várias tecnologias de fabricação (TTL normal, LS, S, F, CMOS etc). Numa mesma pastilha de circuito integrado, dependendo do tipo de biestável e de tecnologia de fabricação, encontram-se desde um até dezesseis biestáveis.

Na tabela VI listam-se alguns biestáveis integrados da família TTL normal.

Código do Função Borda (ou nível) de atuação do relógio dispositivo Quad D Latch 7475 NÍVEL UM Quad RS Latch (não tem relógio) 74279 16-bit D Latch 74170 NÍVEL ZERO Dual D 7474 BORDA DE SUBIDA (↑) Quad D BORDA DE SUBIDA (↑) 74175 Dual J-K 74LS73 MESTRE-ESCRAVO-BORDA DE DESCIDA (↓) 7470 Single J-K BORDA DE SUBIDA (↑) Dual J-K 74LS107 BORDA DE DESCIDA (↓) Dual J-K 74109 BORDA DE SUBIDA (↑)

Tabela VI - Alguns Tipos de Biestáveis TTL Integrados.

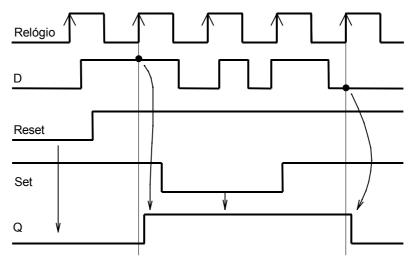

Em praticamente todos os biestáveis integrados (exceto nos tipos RS), além dos sinais de controle e do sinal de relógio, são disponíveis entradas assíncronas de *set* e *reset*. Essas entradas têm prioridade sobre todas as outras e, enquanto acionadas, impõem na saída Q o nível lógico 1 (*set*) ou o nível lógico 0 (*reset*), independentemente do valor do sinal do relógio e das entradas de controle (J-K, ou D).

Por exemplo, no biestável integrado 7474 (tipo D), há as entradas set e reset negativas que permitem que o relógio atue apenas quando ambas são iguais a 1, conforme mostra a figura 1.16.

Nos manuais dos fabricantes de circuitos integrados é possível verificar como as configurações mostradas, por exemplo, nas Figuras 1.10 (CI 7474) e 1.12 (CI 74109) se alteram, em função das entradas de set e reset assíncronos.

Figura 1.16 - Entradas de Set e Reset Assíncronas.

## 1.5 Parâmetros de Tempo dos Biestáveis

Pelo fato das portas lógicas utilizadas para construir os biestáveis apresentarem atrasos intrínsecos, existem limitações nos sinais de controle, de relógio e, quando utilizados, nos sinais de set e reset assíncronos. Essas limitações existem tanto para os biestáveis construídos com portas lógicas, quanto para os biestáveis integrados.

Definem-se, a seguir, os parâmetros mais importantes, que se referem principalmente aos circuitos biestáveis:

- **f**<sub>max</sub>: máxima freqüência do sinal do relógio. Acima dessa freqüência o comportamento do dispositivo é imprevisível.

- **t**<sub>w</sub>: largura de pulso dos sinais de entrada (de relógio, de *set* e *reset* assíncronos); geralmente é imposta uma largura mínima.

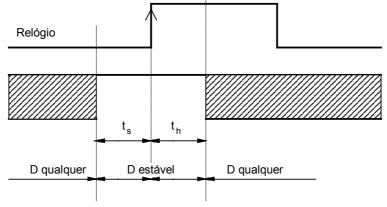

- **t**<sub>h</sub>: hold time ou tempo de manutenção: é o intervalo de tempo imediatamente após a borda de atuação do relógio (ou imediatamente após o instante em que o sinal do relógio atingiu o seu nível de atuação) durante o qual os sinais de controle (J, K, D) devem permanecer estáveis para garantir o funcionamento correto.

- t<sub>s</sub>: set-up time ou tempo de preparação: é o intervalo de tempo imediatamente anterior à borda de atuação do sinal de relógio (ou imediatamente anterior ao instante em que o sinal do relógio atingiu o seu nível de atuação) durante o qual os sinais de controle (J, K, D) devem permanecer estáveis, para serem copiados corretamente na saída Q.

Além dos parâmetros mencionados, os circuitos biestáveis integrados possuem todos os parâmetros específicos da família a que pertencem, como os relativos aos níveis de tensão de entrada e de saída, de **fan-in** e **fan-out** e de tempo de propagação (atraso).

Na figura 1.17 mostra-se, para o circuito integrado 7474 (flip-flop tipo D), o significado de  $t_h$  e  $t_s$ .

Figura 1.17 - Tempos de Preparação e de Manutenção.

#### ${\sf EPUSP\ -\ PCS\ 2011/2305/2355\ -\ Laborat\'orio\ Digital}$

Existem outros dispositivos, que não biestáveis, onde os parâmetros  $\mathbf{t_s}$  e  $\mathbf{t_h}$  também são pertinentes. Em alguns dispositivos tais parâmetros podem assumir valores negativos ( $\mathbf{t_h}$  negativo significa que o sinal pode deixar de ser estável antes da borda ocorrer;  $\mathbf{t_s}$  negativo significa que o sinal pode ficar estável apenas após a borda ocorrer e ainda ser reconhecido).